3-bit Magnitude Comparator using logic gates

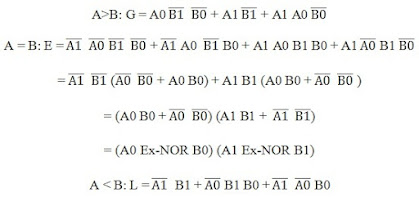

A 3-bit comparator which is designed using logic gates E.g. XNOR, OR, AND etc.

The code was tested using a test-bench code which tested the design for all the 81 combinations of inputs.

library IEEE;use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity comparator is

port( a,b : in unsigned(2 downto 0); --3 bit numbers that are to be compared

a_equal_b : out std_logic; --a is equal to b

a_less_b : out std_logic; --a is less than b

a_greater_b : out std_logic --a is greater than b

);

end comparator;

architecture gate_level of comparator is

signal w1,w2,w3,w4,w5,w6,w7,w8,w9 : std_logic := '0';

BEGIN

w1 <= not(a(2) xor b(2)); --XNOR-gate with 2 inputs.

w2 <= not(a(1) xor b(1)); --XNOR-gate with 2 inputs.

w3 <= not(a(0) xor b(0)); --XNOR-gate with 2 inputs.

w4 <= (not a(2)) and b(2);

w5 <= (not a(1)) and b(1);

w6 <= (not a(0)) and b(0);

w7 <= a(2) and (not b(2));

w8 <= a(1) and (not b(1));

w9 <= a(0) and (not b(0));

a_equal_b <= w1 and w2 and w3; -- a is equals to b.

a_less_b <= w4 or (w1 and w5) or (w1 and w2 and w6); -- a is less than b

a_greater_b <= w7 or (w1 and w8) or (w1 and w2 and w9); -- a is greater than b

end gate_level;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY t_b IS

END t_b;

ARCHITECTURE behavior OF t_b IS

--Inputs

signal a : unsigned(2 downto 0) := (others => '0');

signal b : unsigned(2 downto 0) := (others => '0');

--Outputs

signal a_equal_b : std_logic;

signal a_less_b : std_logic;

signal a_greater_b : std_logic;

signal x,y : integer;

BEGIN

uut: entity work.comparator PORT MAP (

a => a,

b => b,

a_equal_b => a_equal_b,

a_less_b => a_less_b,

a_greater_b => a_greater_b

);

stim_proc: process

begin

for x in 0 to 8 loop

for y in 0 to 8 loop

a <= to_unsigned(x,3);

b <= to_unsigned(y,3);

wait for 10 ns;

end loop;

end loop;

end process;

END;